### **Spatial Computation**

Mihai Budiu December 2003 CMU-CS-03-217

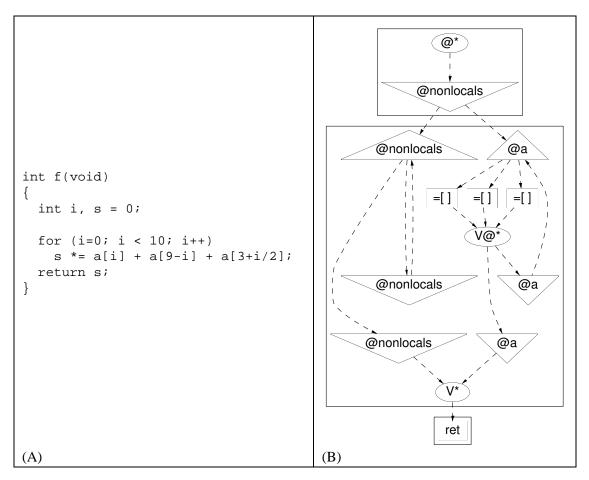

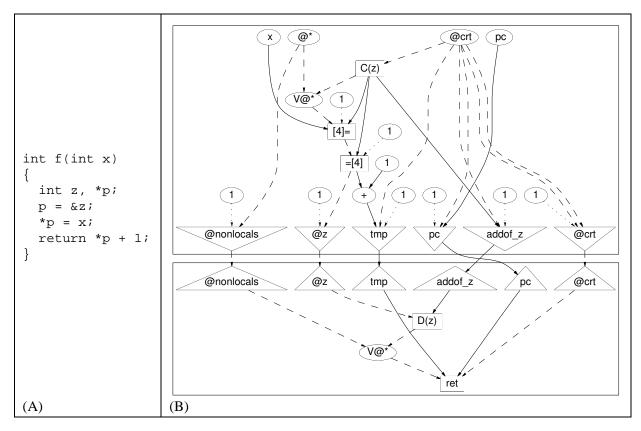

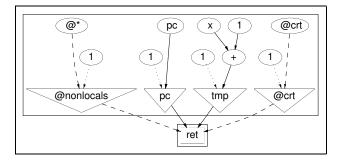

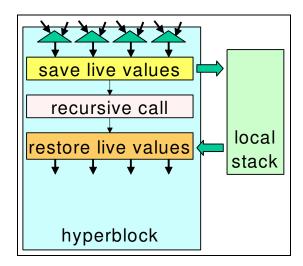

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Thesis Committee:**

Seth Copen Goldstein, Chair Peter Lee Todd Mowry Babak Falsafi, ECE Nevin Heinze, Agere Systems

This research was sponsored by the Defense Advanced Projects Agency (DARPA) under US Army contract no. DABT6396C0083, DARPA under US Navy grant no. N000140110659 via Pennsylvania State University and via Hewlett-Packard (HP) Laboratories, the National Science Foundation (NSF) under grant no. CCR-0205523 and no. CCR-9876248, and by generous donations from the Altera Corporation and HP. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the sponsors or any other entity.

## **Abstract**

This thesis presents a compilation framework for translating ANSI C programs into hardware dataflow machines. The framework is embodied in the CASH compiler, a Compiler for Application-Specific Hardware. CASH generates asynchronous hardware circuits that directly implement the functionality of the source program, without using any interpretative structures. This style of computation is dubbed "Spatial Computation." CASH relies extensively on predication and speculation for building efficient hardware circuits.

The first part of this document describes Pegasus, the internal representation of CASH, and a series of novel program transformations performed by CASH. The most notable of these are a new optimal register-promotion algorithm and partial redundancy elimination for memory accesses based on predicate manipulation.

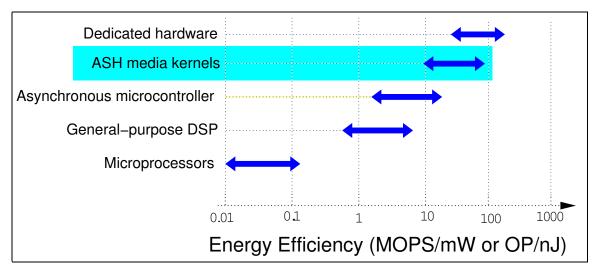

The second part of this document evaluates the performance of the generated circuits using simulation. Using media processing benchmarks, we show that for the domain of embedded computation, the circuits generated by CASH can sustain high levels of instruction level parallelism, due to the effective use of dataflow software pipelining. A comparison of Spatial Computation and superscalar processors highlights some of the weaknesses of our model of computation, such as the lack of branch prediction and register renaming. Low-level simulation however suggests that the energy efficiency of Application-Specific Hardware is three orders of magnitude better than superscalar processors, one order of magnitude better than low-power digital signal processors and asynchronous processors, and approaching custom hardware chips.

The results presented in this document can be applied in several domains: (1) most of the compiler optimizations are applicable to traditional compilers for high-level languages; (2) CASH itself can be used as a hardware synthesis tool for very fast system-on-a-chip prototyping directly from C sources; (3) the compilation framework we describe can be applied to the translation of imperative languages to dataflow machines; (4) we have extended the dataflow machine model to encompass predication, data-speculation and control-speculation; and (5) the tool-chain described and some specific optimizations, such as lenient execution and pipeline balancing, can be used for synthesis and optimization of asynchronous hardware.

# **Contents**

| 1 | Intr | oduction                                              | 1  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Motivation                                            | 1  |

|   | 1.2  | Application-Specific Hardware and Spatial Computation | 2  |

|   |      | 1.2.1 ASH and Computer Architecture                   | 5  |

|   | 1.3  | Research Approach                                     | 5  |

|   | 1.4  | Contributions                                         | 6  |

|   |      | 1.4.1 Thesis Statement                                | 7  |

|   | 1.5  | Thesis Outline                                        | 7  |

| Ι | Cor  | npiling for Application-Specific Hardware             | 9  |

| 2 | CAS  | SH: A Compiler for Application-Specific Hardware      | 11 |

|   | 2.1  | Overview                                              | 11 |

|   | 2.2  | The Virtual Instruction Set Architecture              | 12 |

|   | 2.3  | Compiler Structure                                    | 13 |

|   |      | 2.3.1 Front-End Transformations                       | 14 |

|   |      | 2.3.2 Core Analyses and Transformations               | 15 |

|   |      | 2.3.3 Back-Ends                                       | 17 |

|   | 2.4  | Optimizations Overview                                | 17 |

|   |      | 2.4.1 What CASH Does Not Do                           | 17 |

|   |      | 2.4.2 What CASH Does                                  | 19 |

|   | 2.5  | Compiling C to Hardware                               | 19 |

|   |      | 2.5.1 Using C for Spatial Computation                 | 19 |

|   |      | 2.5.2 Related Work                                    | 20 |

|   |      | 2.5.3 Limitations                                     | 22 |

|   | 2.6  | Code Complexity                                       | 23 |

|   | 2.7  | Compilation Speed                                     | 23 |

| 3 | Pega | asus: a Dataflow Internal Representation              | 27 |

|   | 3.1  | Introduction                                          | 27 |

|   |      | 3.1.1 Summary of Pegasus Features                     | 28 |

|   |      | 3.1.2 Related Work                                    | 29 |

|   | 3.2  | Pegasus Primitives                                    | 30 |

|   |      | 3.2.1 Basic Model                                     | 30 |

|   |      | 3.2.2          | Data Types                                             |

|---|------|----------------|--------------------------------------------------------|

|   |      | 3.2.3          | Operations                                             |

|   | 3.3  | Buildin        | g Pegasus Representations                              |

|   |      | 3.3.1          | Overview                                               |

|   |      | 3.3.2          | Input Language: CFGs                                   |

|   |      | 3.3.3          | Decomposition in Hyperblocks                           |

|   |      | 3.3.4          | Block and Edge Predicates                              |

|   |      | 3.3.5          | Multiplexors                                           |

|   |      | 3.3.6          | Predication                                            |

|   |      | 3.3.7          | Speculation                                            |

|   |      | 3.3.8          | Control-Flow                                           |

|   |      | 3.3.9          | Token Edges                                            |

|   |      |                | Prologue and Epilogue Creation                         |

|   |      |                | Handling Recursive Calls                               |

|   |      |                | Program Counter, Current Execution Point               |

|   |      |                | Switch Nodes                                           |

|   | 3.4  |                | ements                                                 |

|   | 3.4  | Measur         |                                                        |

| 4 | Prog | gram Op        | otimizations 5                                         |

|   | 4.1  | -              | ction                                                  |

|   | 4.2  |                | zation Order                                           |

|   | 4.3  | _              | al Optimizations                                       |

|   |      | 4.3.1          | Free Optimizations                                     |

|   |      | 4.3.2          | Term-Rewriting Optimizations                           |

|   |      | 4.3.3          | Other Optimizations                                    |

|   |      | 4.3.4          | Induction Variable Analysis                            |

|   |      | 4.3.5          | Boolean Minimization                                   |

|   | 4.4  |                | Redundancy Elimination for Memory                      |

|   | 7.7  | 4.4.1          | An Example                                             |

|   |      | 4.4.2          | Increasing Memory Parallelism                          |

|   |      | 4.4.3          | Partial Redundancy Elimination for Memory              |

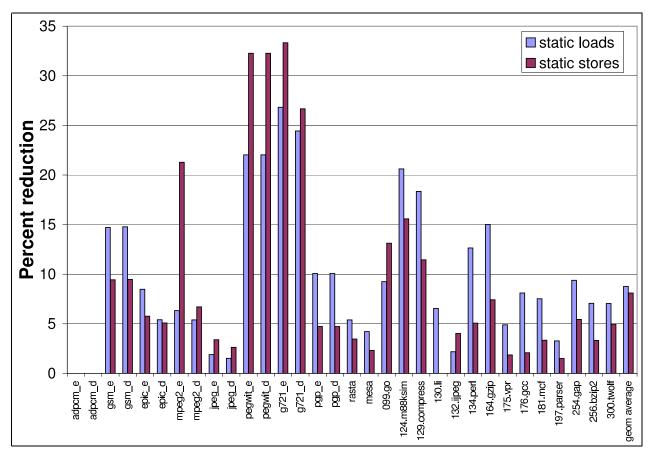

|   |      | 4.4.4          | Experimental Evaluation                                |

|   | 4.5  |                | •                                                      |

|   | 4.5  |                |                                                        |

|   |      | 4.5.1<br>4.5.2 |                                                        |

|   |      |                | Fine-Grained Memory Tokens                             |

|   |      | 4.5.3          | Using Address Monotonicity                             |

|   | 1.0  | 4.5.4          | Dynamic Slip Control: Loop Decoupling                  |

|   | 4.6  | -              | l Inter-Iteration Register Promotion                   |

|   |      | 4.6.1          | Preliminaries                                          |

|   |      | 4.6.2          | Conventions                                            |

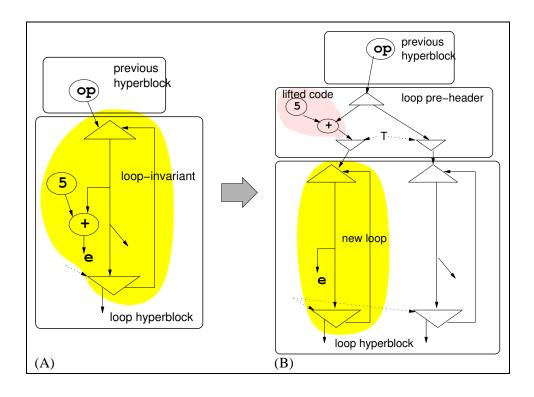

|   |      | 4.6.3          | Scalar Replacement of Loop-Invariant Memory Operations |

|   |      | 4.6.4          | Inter-Iteration Scalar Promotion                       |

|   |      | 4.6.5          | Implementation                                         |

|   |      | 4.6.6          | Handling Loop-Invariant Predicates                     |

|   |      | 4.6.7          | Discussion                                             |

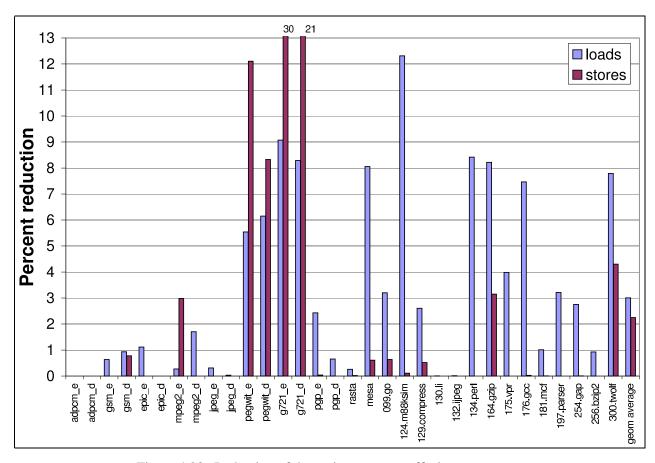

|   |      | 4.6.8          | Experimental Evaluation                                |

|    | 4.7  | Dataflow Analyses on Pegasus        | 111        |

|----|------|-------------------------------------|------------|

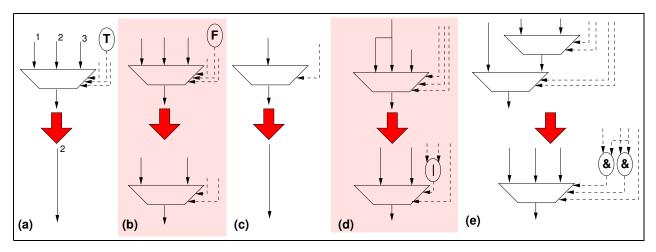

|    |      | 4.7.1 Global Constant Propagation   | 112        |

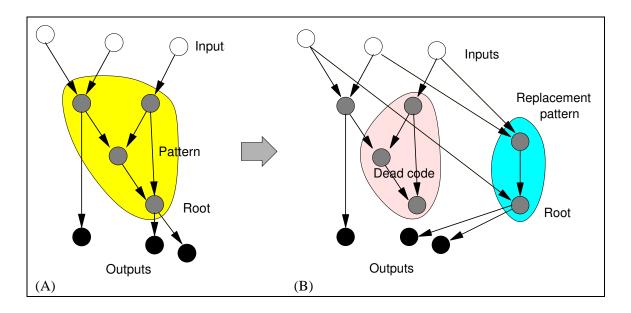

|    |      | 4.7.2 Dead Code Elimination         | 114        |

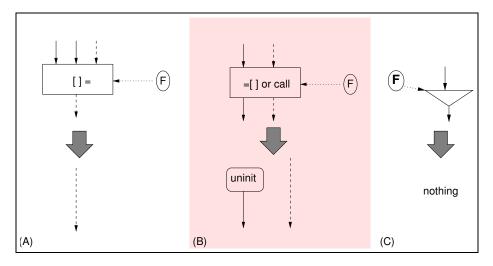

|    |      | 4.7.3 Dead Local Variable Removal   | 114        |

|    |      |                                     |            |

| 5  | _    |                                     | 117        |

|    | 5.1  |                                     | 117        |

|    | 5.2  | e                                   | 120        |

|    | 5.3  | Debugging Support                   | 120        |

|    | 5.4  | Coding in C++                       | 121        |

|    |      |                                     |            |

| II | 4 6  | SH at Run-time                      | 123        |

| 11 | AS   | on at Kun-time                      | 143        |

| 6  | Pega | asus at Run-Time                    | 125        |

| Ū  | 6.1  |                                     | 125        |

|    | 0.1  | •                                   | 125        |

|    | 6.2  |                                     | 127        |

|    | 6.3  |                                     | 127<br>127 |

|    | 0.5  | •                                   | 128        |

|    | 6.4  |                                     | 130        |

|    | 6.5  |                                     | 132        |

|    | 0.5  |                                     | 133        |

|    |      |                                     | 133        |

|    |      |                                     | 134        |

|    | 6.6  |                                     | 135        |

|    | 6.7  | ·                                   | 136        |

|    | 0.7  | · · · ·                             | 138        |

|    |      |                                     | 139        |

|    | 6.8  | 1                                   | 146        |

|    | 0.0  |                                     |            |

| 7  | ASE  | I in Embedded Systems               | 147        |

|    | 7.1  | Introduction                        | 147        |

|    | 7.2  | Hardware-Software Partitioning      | 148        |

|    | 7.3  | Pointer Independence                | 149        |

|    | 7.4  | Evaluation                          | 150        |

|    |      | 7.4.1 Kernels                       | 151        |

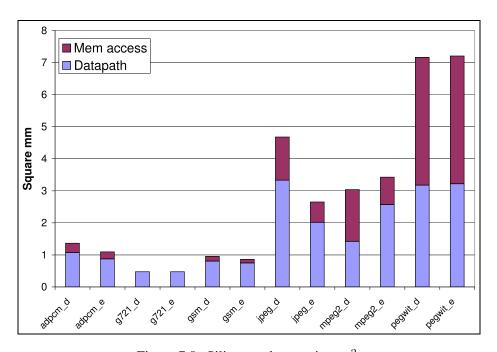

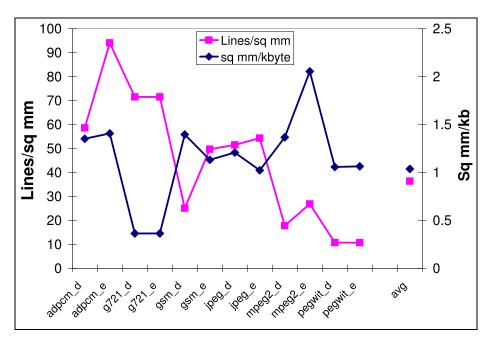

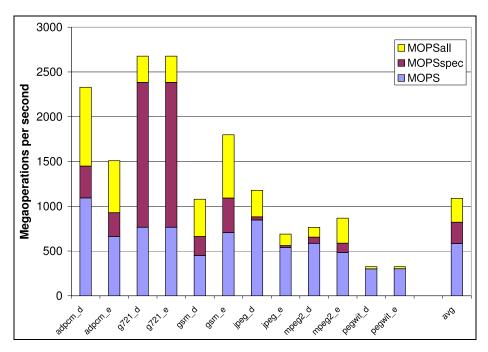

|    |      | 7.4.2 Performance Results           | 151        |

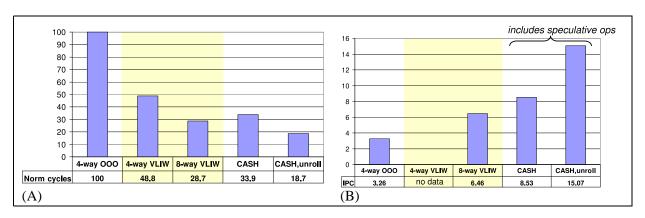

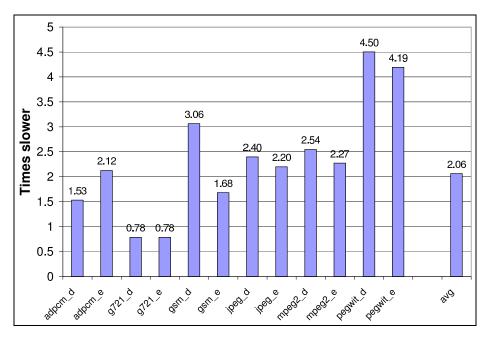

|    |      | 7.4.3 Comparison to a VLIW          | 155        |

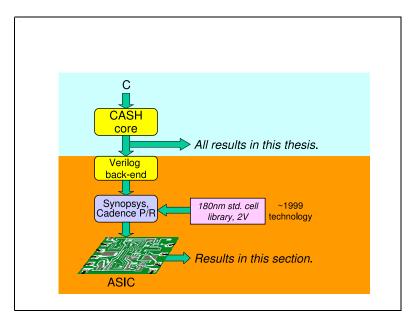

|    | 7.5  | All the Way to Verilog              | 156        |

|    |      |                                     | 159        |

|    |      | 7.5.2 Execution performance         | 159        |

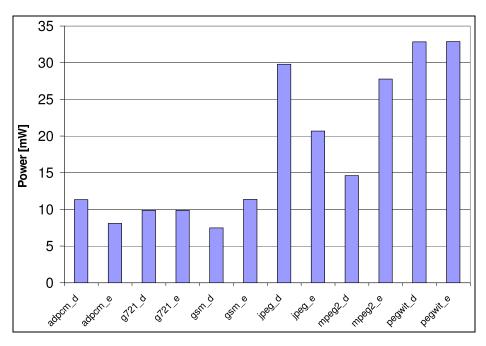

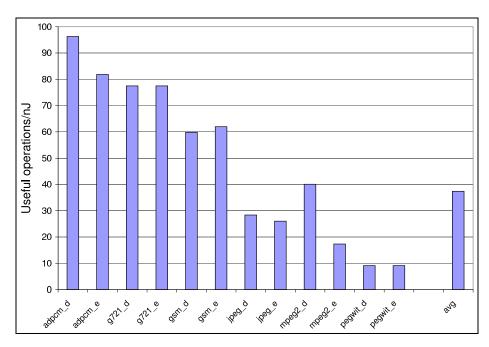

|    |      | 7.5.3 Power and Energy              | 161        |

|    |      | 7.5.4 Impact of Future Technologies | 164        |

|    | 7.6  |                                     | 16/        |

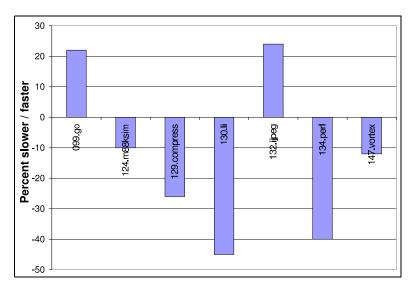

| 8  | Spat | tial Computation and Superscalar Processors                       | 165 |

|----|------|-------------------------------------------------------------------|-----|

|    | 8.1  | Introduction                                                      | 165 |

|    |      | 8.1.1 Spatial Computation Strengths                               | 165 |

|    |      | 8.1.2 Superscalar Processor Strengths                             | 166 |

|    | 8.2  | ASH versus SuperScalar                                            | 167 |

|    |      | 8.2.1 Performance Measurements                                    | 167 |

|    |      | 8.2.2 Critical Code Segments                                      | 167 |

|    | 8.3  | A Limit-Study with Perfect Branch Prediction                      | 177 |

|    | 8.4  | A Design for Integrating Branch Prediction in Spatial Computation | 178 |

|    |      | 8.4.1 Compiler-Controlled Dataflow Speculation                    | 179 |

|    |      | 8.4.2 Comments                                                    | 180 |

|    | 8.5  | Conclusions                                                       | 181 |

| 9  | Exte | ensions and Future Work                                           | 183 |

|    | 9.1  | Building a Complete System                                        | 183 |

|    | 9.2  | Hardware Support for ASH                                          | 183 |

|    | 9.3  | Cross-Breeding ASH and Processors                                 | 184 |

| 10 | Con  | clusions                                                          | 187 |

| 11 | Epil | ogue                                                              | 189 |

| A  | Bene | chmarking Methodology                                             | 191 |

| В  | Cor  | rectness Arguments                                                | 193 |

|    | B.1  | Invariants                                                        | 193 |

|    | B.2  | Properties                                                        | 194 |

|    | B.3  | Speculative Computation Gives Correct Results                     | 195 |

|    | B.4  | Formal Semantics                                                  | 196 |

|    | Bilb | liography                                                         | 200 |

# **Chapter 1**

# Introduction

#### 1.1 Motivation

For most computer users the speed and capabilities of today's computer systems were unthinkable as little as a decade ago. The relentless advance of technology at an exponential pace for more than 40 years has produced amazingly complex and powerful machines – in September 2003 Intel released the Itanium 2 processor for servers, built out of 410 million transistors on a single 374mm<sup>2</sup> chip and consuming 130W. A desktop microprocessor with more than 1 billion transistors is expected by 2007. The exponential increase in computing resources is expected to last at least another decade, and perhaps even more if the promises of nanotechnology come true.

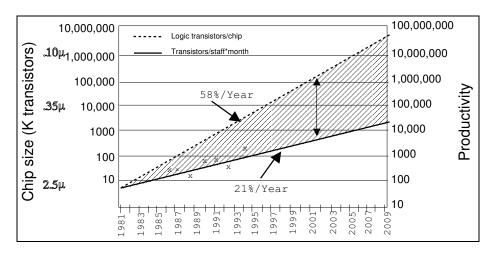

However, all this progress has come at a cost. The very success of miniaturization creates new unexpected obstacles. Figure 1.1 illustrates one such difficulty: the complexity of the hardware design increases with the number of transistors, at an exponential pace [itr99]. For instance, the complexity of a hardware design depends on the number of *exceptions* that cannot be automatically handled by Computer-Aided Design (CAD) tools [HMH01]; the number of these exceptions grows with the number of transistors. Although the productivity of hardware designers increases too, due to improvements in CAD tools, it does so at a slower pace. The end result is a growing *productivity gap* between what we have and what we can economically use. Fewer and fewer companies can close this gap, and when they do, they employ larger and larger design, test, verification and manufacturing teams.

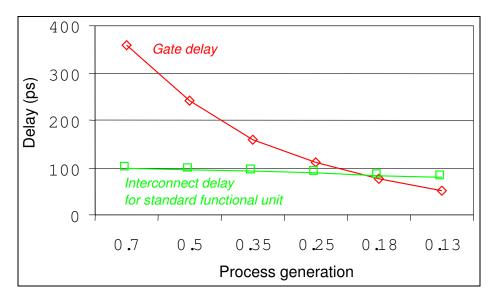

The problems of hardware design productivity are nowhere near being solved. In fact, more ominous obstacles are surfacing. Figure 1.2 shows the signal propagation delay through logic gates and "average-sized" wires. Since many structures of a modern processor such as the forwarding paths on the pipeline, the multi-ported register files, the instruction wake-up logic, etc., require global signals (i.e., spanning multiple modules), there simply is not enough time for the signals to propagate along these wires at very high clock speeds. In fact, at 10GHz a signal can cover less than 1% of the surface of a chip in one clock cycle [AMKB00], making any architecture relying on global signals infeasible.

The research presented in this document is aimed directly at these problems. We explore (**A**) a new computational model which requires no global synchronization, and (**B**) a new CAD methodology aimed at bridging both software compilation and microarchitecture. Our model is named Spatial Computation. In Spatial Computation, applications written in high-level languages are compiled directly into hardware circuits. The synthesized circuits feature only localized communication, require no broadcast, no global control, and are timing-insensitive, and therefore correct even when the communication latency is not statically predictable. The compiler we have developed requires no designer intervention (i.e., it is fully automatic),

Figure 1.1: Complexity and productivity versus technology generation.

Figure 1.2: Wires and not gates dominate the delay in advanced technologies.

is fast, and exploits both instruction-level parallelism and pipelining. This thesis is an investigation of the compilation methodology and of the properties of the synthesized circuits.

## 1.2 Application-Specific Hardware and Spatial Computation

One can view Spatial Computation in several ways:

- As a pre-von Neumann model of computation [vN45]: a computer which has no stored program in the form of a sequence of instructions. In this sense, ASH is a big automatically-generated Application-Specific Integrated Circuit (ASIC).

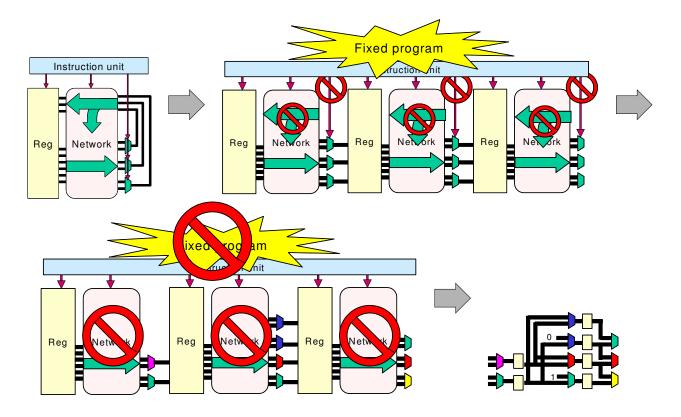

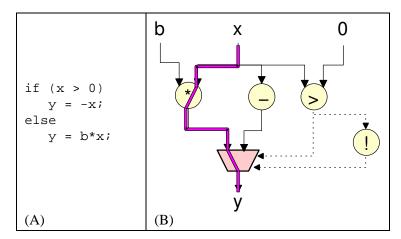

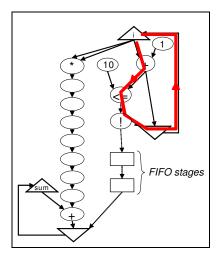

- As a *specialization* of the pipeline of a processor through the "unrolling" and "constant folding" of a fixed program, as illustrated in Figure 1.3.

Figure 1.3: ASH can be seen as the unrolling and specialization of the pipeline of a traditional wide processor, by removing the forwarding paths, specializing the type and number of functional units, simplifying the interconnection network to point-to-point links, removing the global register file and instruction issue logic.

• As the limit result of clustering a very long instruction-word (VLIW) processor with a virtually unlimited instruction word.

From an architectural point of view Spatial Computation exhibits some desirable attributes:

- It is *program-specific* and therefor it has no interpretation overhead.

- It can exploit virtually unlimited instruction-level parallelism (ILP).

- It features mostly short and fast point-to-point wires driven by a single writer each (i.e., wires that require no arbitration).

- It is asynchronous and therefore latency tolerant. This makes it correct by design, even when it employs global structures, such as the memory access network.

- As in superscalar processors and dataflow machines, its computation is dynamically scheduled, based on the availability of data.

- It requires no centralized control structures.

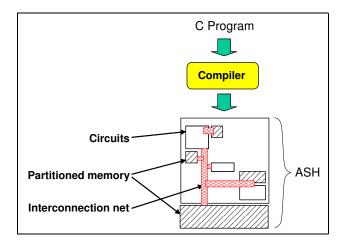

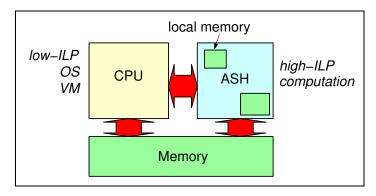

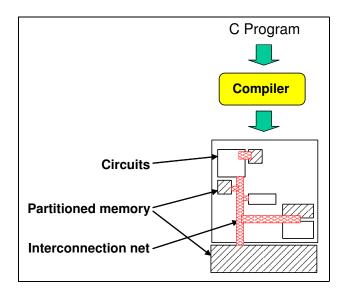

Figure 1.4: Application-Specific Hardware is generated by the automatic synthesis of computational structures, memories and an interconnection network from C programs.

- It has a modular structure.

- It is composed of *lean* hardware, in particular, both datapath and control-path contain no broadcast structures, no arbitration, no multi-ported memory or register files, no content-addressable structures, and would therefore be able to run at a very high speed.<sup>1</sup>

- It is easy to reason about. Therefore we believe it is easily amenable to formal verification.

In this thesis we investigate in detail a particular instance of Spatial Computation, with the following features:

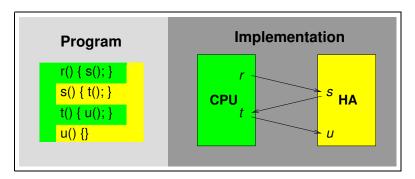

- Each source procedure is translated into a distinct hardware structure.

- Each source operation is synthesized as a different hardware arithmetic unit. As a result, our circuits exhibit *no computational resource sharing*.

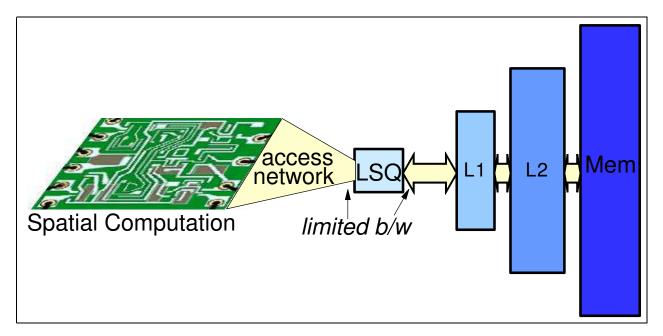

- All program data is stored in a single monolithic memory, accessible through a conventional memory hierarchy, including a load-store queue and caches.

- The synthesized hardware is an application-specific *static dataflow machine*. This means that (1) operations are executed based on the availability of data; and (2) at any point in time there can exist in the circuit at most one result for each operation.<sup>2</sup>

We define Application-Specific Hardware (ASH), as the hardware structure implementing a particular program, synthesized under compiler control from the application source code. The translation is illustrated in Figure 1.4.

From now on, when we use the terms "Spatial Computation" and "ASH" we will only refer to this particular architecture. There can be other reasonable definitions for these terms (e.g., application-specific processor), but here we use these terms with the meanings as defined.

<sup>&</sup>lt;sup>1</sup>However, the memory access network requires some complex structures.

<sup>&</sup>lt;sup>2</sup>In contrast, in dynamic dataflow [AN90], at some point in time, there can be an arbitrary number of results "live" for each operation.

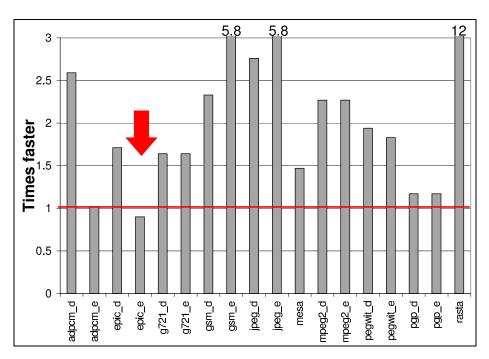

#### 1.2.1 ASH and Computer Architecture

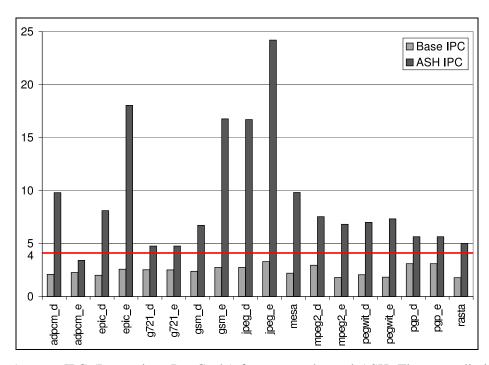

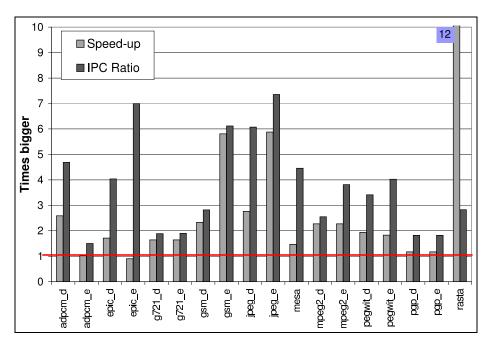

The features of Spatial Computation suggest that it may provide very good performance on data-intensive programs, which have high amounts of instruction-level parallelism. Indeed, as we show in Chapter 7, ASH can surpass by a comfortable margin a 4-wide out-of-order superscalar on media processing kernels.<sup>3</sup>

However, as our analysis shows, some of the strengths of ASH are also its weaknesses when we consider control-intensive programs. The lack of branch prediction in ASH is a severe handicap for benchmarks where the ILP is low and the computation of the branch conditions is on the critical path. The distributed nature of ASH makes reaching memory expensive and squashing speculation difficult.

These behaviors suggest that a versatile computer system should combine the strengths of both outof-order processors for control-intensive code, and Spatial Computation for data-intensive kernels. This research opens the exploration for the detailed architecture of such a system, and mostly of a low-overhead hardware substrate suitable for Spatial Computation (when compared to contemporary FPGA devices [ZRG<sup>+</sup>02]).

### 1.3 Research Approach

A good characterization of this research would be "translating programs to hardware in the absence of resource constraints." This approach is certainly extreme and could be dismissed as relying on unrealistic assumptions. However, we think that there is merit in such a methodology:

First, such an approach forces a change of perspective in treating the problem and may provide fresh

insights into the solution space, allowing one to reconsider methods traditionally excluded. As a

result, even though the constraints are relaxed, such an approach may produce results usable within a

realistic setting.

For example, Spatial Computation blurs the notion of instruction set architecture (ISA). This enabled us to explore the addition of new computational primitives, such as the token generator (whose use is described in Section 4.5.4), which dynamically controls the slip between two loops. The use of this primitive enables a new type of parallelization/pipelining optimization, which we named loop decoupling. An important but subtle aspect of the lack of the ISA is the fact that the computational primitives no longer have to be encoded in fixed-size machine instructions. This enables us to use primitives with a potentially large number of inputs, such as multiplexors or token combine operators (the latter described in Section 4.4). We currently are investigating how the use of primitives similar to token generators in a more traditional multithreaded architecture can enable the same benefits.

The register promotion algorithm from Section 4.6 is the result of a similar shift in the point of view regarding the "layering" of a system: that algorithm takes a traditional compile-time construct — dataflow availability information — and transforms it into a run-time object. This transformation enables an accurate dynamic computation of availability and therefore obtains dynamic optimality of the number of memory accesses. As the computational bandwidth of processors increases, these kinds of optimizations may become more advantageous. In the case of register promotion, the benefit from removing expensive memory operations outweighs the increase in scalar computations to maintain the dataflow information. We named this new kind of dataflow analysis — Static Instantiation, Dynamic Evaluation (SIDE). The compiler statically determines which dataflow facts are beneficial in a run-time computation, and inserts code in the program to dynamically compute the dataflow facts. The register promotion algorithm is the application of the SIDE method to the classical dataflow

<sup>&</sup>lt;sup>3</sup>This is assuming our assumptions for the architectural parameters are realistic.

availability problem. We are currently investigating whether the SIDE methodology can be applied to other dataflow analyses.

Another example of the power of an unconventional framework is shown by the algorithms we have devised for treating memory dependences. In traditional systems, memory dependence information is computed first by the compiler and then completely discarded and re-created dynamically by the processor. So there can be some benefit if the static and dynamic stages can share information. In Spatial Computation the token edges used to ensure memory consistency are both a compile-time and a run-time object. We are currently investigating the benefit of such a scheme in classical architectures.

- 2. Second, while we relax some constraints, we do maintain some hard limits for other parameters. For example, we do not modify the semantics of C, we do not exclude any language constructs, and we do not enforce a particular coding style for programs translated to hardware, as does the vast majority of the research on high-level synthesis from C.

- 3. Third, our results provide understanding on the limits of a particular model of computation, as evidenced in Chapter 8, which compares ASH with superscalar processors.

#### 1.4 Contributions

Even though the research presented in this document is only the beginning of a long-term endeavor, and many more refinements need be made before a complete end-to-end solution is obtained, it still has produced some worthwhile results. To our knowledge, the following points are original research contributions of this work:

- Predicated Static-Single Assignment dataflow internal representation: We are the first to report on the wide scale usage of a compiler internal program representation that brings together static single-assignment, predication, forward speculation and a functional representation of side-effects. Several features of this representation make compiler development particularly efficient: (1) it has precise semantics; (2) enables a succinct expression of most common program optimizations; (3) it enables efficient reasoning about memory state and therefore enables powerful memory optimizations; and (4) it makes dataflow analyses simple and efficient.

- SIDE as a new framework for dataflow analysis: Our new hybrid dataflow analysis framework,

Static Instantiation Dynamic Evaluation, uses code to dynamically evaluate dataflow information when a static evaluation is too conservative.

- New compiler algorithms: We describe new optimization algorithms for redundancy elimination

in memory accesses: register promotion and partial redundancy elimination for memory. We also

describe algorithms for enhancing the pipelining of loops, such as a scheme for pipeline balancing,

memory access pipelining in loops through fine-grained synchronization, and loop decoupling.

- **Language extension:** We have studied the efficiency of user annotations in C programs (through the use of #pragma statements) to convey pointer non-aliasing information to the compiler.

- **Dataflow model extensions:** We have realized the first translation of the complete C language to a dataflow machine. This effort has crystallized a methodology for implementing imperative languages,

including unstructured flow-of-control, recursion, side effects and modifiable storage. We have incorporated predication and speculation in the dataflow model of execution and we have suggested a way to perform the equivalent of branch prediction in dataflow machines. Other contributions to the dataflow model of execution are the use of lenient operations and an enhanced form of pipeline balancing.

- Hardware synthesis: We have built the first complete system able to translate arbitrary C programs

into hardware. This tool differs from most prior approaches in its change of perspective: C is not

regarded as a hardware-description language, destined to describe an independently-executing piece

of hardware. Instead, the goal of the synthesis system is to directly implement a given application as

a hardware circuit.

- Asynchronous circuit design: We have provided the first tool that can be used to translate C programs into asynchronous circuits. The translation methodology is general enough to be applicable to any imperative language.

- Embedded systems construction: We have built the CASH compiler, which can be used as a tool for very fast prototyping of embedded systems hardware accelerators and has shown its effectiveness on a wide range of media processing applications. Although not detailed in this document, we have suggested a new way of performing hardware-software partitioning, which relies on separating the policy from the mechanism. This partitioning is easily amenable to automatization. CASH, together with the partitioning methodology, constitute a very efficient method of exploring the design of complex application-specific system-on-a-chip devices using only the application source code.

- New perspective on superscalars: We have performed a new limit study on the subject of instruction-level parallelism and the effectiveness of architectural features for exploiting it. Namely, by contrasting a static dataflow model with unbounded resources (ASH) against a superscalar processor implementation, we have highlighted the effectiveness of a monolithic architecture at performing memory accesses, prediction and speculation, and emulating a full dynamic dataflow model of execution.

#### 1.4.1 Thesis Statement

Software compilation technology for targeting predicated architectures can be naturally adapted for performing the automatic synthesis of application-specific, custom hardware dataflow machines. This compilation methodology translates media processing kernels into hardware with a high degree of instruction-level and pipeline parallelism. However, the resulting distributed computation structures are not as easily amenable as traditional monolithic superscalar processors at using acceleration mechanisms such as (correlated) prediction, speculation and register renaming. The lack of these mechanisms is a severe handicap when executing control-intensive code.

#### 1.5 Thesis Outline

This document has been divided into two parts. Part I, encompassing chapters 2–5, is concerned with the "static" aspects of ASH, i.e., compilation. Chapter 2 is a broad overview of the compilation process. Chapter 3 describes in detail Pegasus, the internal representation of the CASH compiler and the process of building it starting from a control-flow graph. Chapter 4, the most substantial of this thesis, is devoted to a

description of the program transformations performed on Pegasus with the goal of increasing performance. Chapter 5 is a collection of advice for other developers of research compilers.

Part II of this thesis, encompassing chapters 6–8, is about the dynamic behavior of ASH. Chapter 6 looks at some emergent properties of the execution of ASH fabrics and discusses some particular optimizations that are only applicable for such a model of computation. A particularly important subject covered is dataflow software pipelining, the main source of parallelism exploited in Spatial Computation. The next two chapters are all about performance. Chapter 7 uses ASH to implement kernels for embedded-type benchmarks and compares its speed with both VLIW and superscalar processors. It also evaluates the performance of the generated circuits using low-level Verilog simulations. Chapter 8 dwells on the hypothetical capabilities of ASH for executing complete control-intensive programs, and contrasts those capabilities with the ones available in a superscalar processor.

Appendix A describes briefly our benchmarking methodology. Appendix B contains both some correctness arguments about the behavior of ASH and a formal definition of the semantics of all its computational primitives.

# Part I

# Compiling for Application-Specific Hardware

# Chapter 2

# CASH: A Compiler for Application-Specific Hardware

This chapter is devoted to a bird's eye view of CASH, the compiler translating C programs into Application-Specific Hardware (ASH). While the subsequent chapters go into many more details, the material here justifies some of the design decisions and describes the compilation process end-to-end.

#### 2.1 Overview

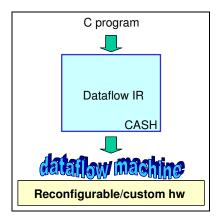

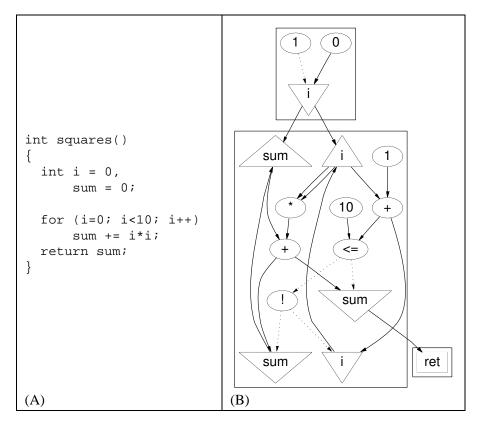

Figure 2.1 shows CASH within its environment. The inputs to the compiler are programs written in ANSI C.<sup>1</sup> CASH represents the input program using a dataflow internal representation called Pegasus. The output of CASH is a custom hardware dataflow machine which directly executes the input program. The result can be implemented either as a custom hardware device or on a reconfigurable hardware substrate.

We envision two different uses for CASH:

- CASH can be used as a pure CAD tool, using C as a hardware description language (HDL) and generating a complete hardware implementation of a program. An evaluation of CASH from this perspective is given in Chapter 8.

- CASH can be used as a piece of a more complex tool-chain targeting a hybrid system-on-a-chip. CASH can then be used to translate selected parts of a larger C program into hardware. The remaining code is executed on a traditional microprocessor, relatively tightly coupled with the custom hardware. Chapter 7 analyses the effectiveness of this configuration.

CASH translates the input program into a flat computational structure which contains no interpretation engine. Roughly, to each operation in the source corresponds one arithmetic unit in the output circuit. This kind of computation structure is called Spatial Computation. It exhibits maximum parallelism and minimal resource sharing. The only resource sharing is at the procedure level since different calls to the same procedure re-use the same circuit.

Currently CASH translates each procedure of a program into a different, completely independent computational circuit. However, by using inlining and by writing carefully crafted library functions<sup>2</sup> one can control to some degree the sharing of the structures in the resulting circuit.

<sup>&</sup>lt;sup>1</sup>The Kernighan & Ritchie dialect mostly works, but may cause occasional difficulties.

<sup>&</sup>lt;sup>2</sup>For example, by implementing all floating-point operations as library calls.

Figure 2.1: The CASH compiler translates C programs into hardware.

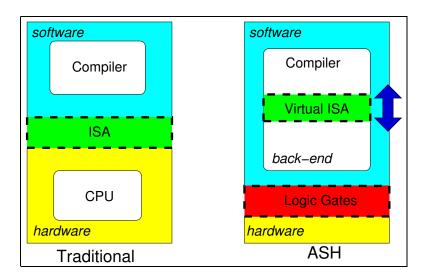

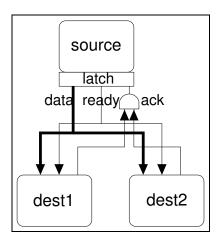

Figure 2.2: The interface between hardware and software in traditional settings and in ASH.

#### 2.2 The Virtual Instruction Set Architecture

Figure 2.2 shows the relationship between hardware and software in two settings: the traditional processor-centric world to the left and ASH to the right. In the traditional setting the software and hardware worlds are separated clearly by the Instruction Set Architecture (ISA), which is a tight contract between the two worlds. The ISA is basically the set of machine instructions recognized by the CPU. The compiler has to express any program as a combination of these instructions. The traditional ISAs are quite rigid, producing a "tyranny of the ISA": even if the compiler has more knowledge about the application at hand, it has no way to send this information to the hardware. Rebellion against this tyranny is quite difficult, as illustrated by the case of the Itanium microprocessors. These processors were designed to accommodate advances in compiler technologies, and therefore required radically different ISAs compared to the traditional x86 processors manufactured by the same company. Intel has needed more than 20 years to decide to switch to this new ISA, despite known shortcomings in the x86 processors. Mistakes in the design of an ISA are very hard to fix.

This state of affairs changes completely in ASH, as shown to the right in Figure 2.2. The interface

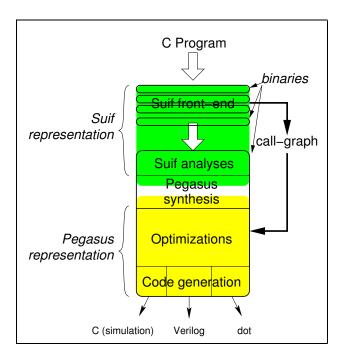

Figure 2.3: The CASH compiler is composed of a Suif front-end for carrying out parsing and high-level optimizations and a custom back-end using a new internal representation called Pegasus.

exposed by the hardware is composed of raw computation gates. This frees, but also complicates, the compilation process. In order to handle the great semantic gap between the source code and the target machine our approach consists in building a "virtual ISA." This time the ISA is entirely a compile-time notion. Think of the virtual ISA as the set of computational primitives the compiler uses to express the meaning of the program. In our setting the virtual ISA is the interface between the compiler core and the back-ends. Unlike in the traditional setting, the virtual ISA is not bound by any rules and can be changed. CASH's virtual ISA is the set of computation primitives of the Pegasus intermediate representation, described in Section 3.2. While virtual ISA resembles a traditional ISA in many respects, it also features substantial differences. For example, it is not bound by machine resources, i.e., does not require a fixed encoding (say, 32 bits) for each instruction. Second, it may be changed by the compiler implementer without touching the external hardware/software interface. The Pegasus virtual ISA contains constructs usually not found in traditional processors, such as a direct representation of memory dependences, described in Section 3.2.3.5. Exploring the space of virtual ISAs may be a rich and rewarding research activity, which may also suggest improvements to traditional ISAs.

## 2.3 Compiler Structure

The CASH compiler is a tool-chain consisting of a Suif-based [WFW<sup>+</sup>94] front-end, a custom-developed core, and several back-ends tightly integrated with the core, all tied together by Perl scripts and Makefiles, as shown in Figure 2.3. Occasionally we will refer to the core also as CASH.

CASH is built on top of the Suif 1 infrastructure — the code base is Suif 1.3.0.5. No optimizations are used from the original Suif distribution. The only functionality used consists in parsing and un-parsing, linking, and basic object manipulation of symbol tables, instructions and static data initializers. All major

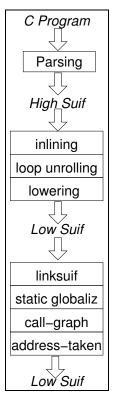

Figure 2.4: Suif front-end structure. The passes communicate with each other through Suif files.

Suif optimizations and analyses used in CASH are locally developed (however, as described below, some are borrowed from different research groups).

#### 2.3.1 Front-End Transformations

The front-end is composed of multiple Suif compilation passes built as separate executables communicating through Suif files. Figure 2.4 shows the transformations performed in the front-end. The front-end will be rarely mentioned in this document.

- Parsing is performed by the Suif driver scc. It is invoked without any optimizations. The result of parsing are high-Suif representation files (i.e., containing high-level constructs, such as for, while loops and if statements, nested scopes and array accesses).

- The procedure inlining pass was written by Tim Callahan from Berkeley as part of his GarpCC [CW98] compiler. It is highly configurable, allowing the use of various policies for inlining. Currently we do not perform cross-file inlining, although the pass supports this functionality.

- The loop unrolling was written by Todd Mowry, then at Stanford. It can unroll both while and for loops, both with and without compile-time constant bounds. Loop unrolling has been tuned to aggressively unroll loops, proving very beneficial for embedded-type benchmarks (see Chapter 7).

Currently we do not unroll loops containing function calls<sup>3</sup> or expensive operations, such as division.<sup>4</sup>

- The lowering pass removes all high-level constructs and nested scopes; the result of lowering is low-Suif, roughly a three-operand representation of the original program.

- Linksuif is a Suif pass which unifies the symbol tables of several files allowing them to be used as a unit. It is a prerequisite of the following passes.

- The "static globalization" pass transforms procedure static variables into globals by mangling their names and moving them to the global symbol table. It is solely used to remove the syntactic sugar of static locals, which are just globals with a local visibility.

- The call-graph pass computes a conservative approximation of the program call-graph. The main usage of the call-graph is to detect recursive procedures, which require a more heavyweight approach in CASH. Since call-graph computation for a language with pointers is P-SPACE complete [Wei80], we resort to several approximations. First, the whole program is scanned and all procedures whose address is taken are noted. Second, a flow-sensitive, intra-procedural pointer analysis is used to restrict as much as possible the points-to set of all functions called through pointers. Third, the strong type-based heuristics described in [Atk02] are applied to prune the candidates for each call through pointers. The strongly-connected components are computed these contain exactly the recursive functions. The resulting call-graph is written to a text file and cached (i.e., it is not recomputed unless the source program changes). It is important to note that it is not enough to know which procedures are recursive. It is also necessary to know which call instructions are potentially recursive.

- Finally, the "address-taken" pass is a Suif built-in flow-insensitive analysis, which tags all objects whose address is taken (and global variables as well). Next, all accesses to such objects are transformed to explicit memory loads and stores through pointers. This step clearly separates scalar accesses from ambiguous accesses which can have side-effects.

#### 2.3.2 Core Analyses and Transformations

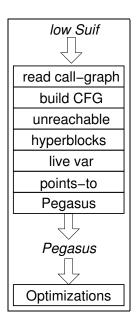

The core of the compiler is the main subject of this thesis. It consists of two parts: a translation from the Suif intermediate representation to our own predicated representation called Pegasus; and the bulk of the program transformations and optimizations, carried on Pegasus. Unlike the front-end, the entire processing of the core and the back-ends are tightly integrated in a single binary executable. Figure 2.5 illustrates the structure of the core.

In order to simplify the build process of the Pegasus representation several analyses are carried out on the three-operand code. Let us briefly discuss them, as shown in the top part of Figure 2.5. The complete implementation of the core was developed by us. It uses some Suif libraries that we have developed to build control-flow graphs and to perform generic dataflow analyses.

• If the call-graph is supplied, it is read at this moment. The call-graph structure is used both to construct the control-flow graph (CFG) and later in the compilation process to synthesize code differently in recursive/non-recursive procedures.

<sup>&</sup>lt;sup>3</sup>There are two reasons for not unrolling loops with function calls: (1) the performance of the unrolled loop cannot be predicted statically; and (2) it changes the pre-computed call-graph of the program.

<sup>&</sup>lt;sup>4</sup>The reason for not unrolling such loops is detailed in Section 6.8.

Figure 2.5: The structure of the core of the compiler.

- Building the CFG is fairly straightforward. However, as described in Section 3.3, some constructs are handled specially; namely, return instructions are always in a basic block of their own, and recursive procedure calls always start a new basic block.

- A simple reachability computation performs unreachable code removal on the CFG.

- The CFG is partitioned into disjoint hyperblocks. This algorithm is based on a depth-first traversal of the CFG and is discussed in Section 3.3.3.

- A live variable computation, which marks for each program point all live scalar variables. There is no lifetime analysis of memory-resident objects, only of the virtual registers.

- A simple pointer analysis is carried out. This step computes a read-write set for each memory access instruction (load, store, call). The set contains symbolic memory locations that may be accessed at run-time by the instruction. For procedure calls it is conservatively assumed that all objects in the read-write set may be modified within the callee and its children.<sup>5</sup> The read-write set is used later during the Pegasus build to insert token edges between non-commuting memory operations (Section 3.3.9).

Since the cost of a points-to analysis can be quite substantial (the space-complexity is  $|CFG| \times |Vars|$ , (i.e., the number of basic blocks multiplied by the number of symbolic objects that can appear in the points-to-sets), a simple heuristic may decide to forgo completely the points-to analysis if the CFG is too large. If this is the case, a very conservative approximation is used instead — all memory operations may access all memory locations. Just a handful of procedures in our benchmarks are too large for pointer analysis.

<sup>&</sup>lt;sup>5</sup>The write-set of a call may be further reduced by using information about arguments qualified with const. But we have not implemented this feature yet.

The actual Pegasus building algorithm is described in detail in Section 3.3, while the Pegasus-based optimizations are covered in detail in Chapter 4. The order of the Pegasus optimizations is the subject of Section 4.2.

#### 2.3.3 Back-Ends

Currently CASH has three back-ends, illustrated in Figure 2.3:

- A dot back-end used to generate drawings of the internal representation of one compiled function. The representation is a fairly simple textual representation of the Pegasus graph in the language of the Graphviz [GN99] graph visualization tool. This "back-end" can be invoked also from a debugger, to print the state of the representation at various points during the compilation process. The dot output has a very simple structure and is easily manipulated by various Perl scripts for debugging and illustrations. The dot tool automatically computes the graph layouts from the textual description. Many of the illustrations in this text were produced in this way. The conventions used for drawing Pegasus representations and some shortcomings of dot are discussed in Section 3.2. The use of this back-end for debugging and performance analysis is further described in Section 5.3, Section 6.3 and Section 6.6.

- A C-simulator back-end is used to generate a relatively high-level simulation of each program. This simulator was used to gather most of the numeric results presented in this document. The simulator models the finite-state machine of each asynchronous operation and is parameterized with operation latencies. However, the simulator ignores the effects caused by the physical layout.

- A Verilog back-end generates direct asynchronous circuits from the Pegasus representation. This back-end was written entirely by Girish Venkataramani.

Most of the translation is fairly straightforward, using libraries for technology mapping each Pegasus primitive. The generation of the memory access network is somewhat complex; the network for handling procedure calls is still under design. The discussion of this back-end is out of the scope of this document. Preliminary measurements using the Verilog code generated by this back-end are presented in Section 7.5. These simulations are more accurate than the ones of the C simulator and do include the effects of the technology mapping libraries and circuit layout.

## 2.4 Optimizations Overview

The rest of this document is only concerned with the core of CASH compiler, as described in Section 2.3.2, operating on the Pegasus representation. In this section we briefly overview the optimizations performed by CASH on the compiled program. A detailed discussion of this topic is the subject of Chapter 4.

#### 2.4.1 What CASH Does Not Do

Before we summarize the optimizations performed, let us mention some optimizations which are *not* part of our compiler.

- A peculiarity of the Pegasus representation is that it is a pure dataflow representation (see Chapter 3). As such, it does not contain any control-flow information.<sup>6</sup> In consequence, many control-flow related optimizations are irrelevant (but see Section 4.1 for a discussion).

- Since CASH targets Spatial Computation, which does not have a fixed instruction set, its back-ends are substantially different from traditional compilers. For instance, CASH does not contain either a register allocator (because we can allocate arbitrarily many registers) or a scheduler (because the circuits synthesized are asynchronous, dynamically scheduled). It also does not contain the lowest level optimizations, such as instruction selection (because we can implement almost any instruction), peephole optimization, or instruction-cache optimizations (because there is no instruction issue in Spatial Computation).

- Although CASH is inspired in many respects from the compilation methodology for Explicitly Parallel Instruction Computing (EPIC) architectures [ACM<sup>+</sup>98], it does not use at all profiling information for guiding its decisions. It is a "pure static" compiler. While the use of profile information would certainly help improve some of the code transformations, it requires a more sophisticated tool-set for mapping back run-time information to the original source-code. We believe that our static approach still provides an interesting reference point in the design space. Some of the features of Spatial Computation, such as lenient execution (see Section 6.4), can make up for the lack of profiling information. Investigating the use of run-time hints for improving Pegasus is an interesting subject of future research.

- CASH is a C compiler. As such it does not implement optimizations which are useless for C programs, such as array bounds checking removal or exception handling. The latter is actually a liberating assumption since C does not really have an exception model, CASH does not implement any (but see Section 2.5.3.1 for a discussion).

- CASH is not a parallelizing compiler. As such, it does not perform any of the loop- and datarestructuring transformations customarily found in parallelizing FORTRAN compilers. The C language is not easily amenable to such transformations.

- CASH does not do any inter-procedural optimizations, except a special handling of recursion and a rather traditional procedure inlining. This is not really a limitation of the model. There is no fundamental reason that inter-procedural analyses and optimizations could not be added to a spatial compiler. This reflects our belief that scalable compilation methodology has to be modular and to support separate compilation. We think that the need for interprocedural analysis and optimization actually reflects a source language shortcoming. In Section 7.3 we explore the way a simple language extension (through the use of a C #pragma statement) can be used to supplant expensive interprocedural aliasing information.

- While CASH tries to exploit parallelism at the program level, it still does too little in exploiting it at the memory level. We expect that reorganizing data layout can provide substantial benefits [SSM01, BRM+99]. However, the C language makes such optimizations difficult, since memory layout has

<sup>&</sup>lt;sup>6</sup>However, a compiler targeting a traditional machine could, with little difficulty, reconstruct a control-flow representation from Pegasus. Predication is deeply enmeshed in Pegasus and therefore targeting an architecture without direct support for predication would probably be rather suboptimal.

<sup>&</sup>lt;sup>7</sup>However, we do plan to add some scheduling-related optimizations, i.e., optimizations taking into account the expected execution order of the operations.

to be exactly preserved for all objects for which some program accesses cannot be disambiguated at compile-time.

• Finally, CASH could do much more in terms of hardware-targeted optimizations. The BitValue analysis [BSWG00], which discovers useless bits in C programs and can narrow the size of the words computed on, is not yet integrated into CASH. Many important hardware-related optimizations are relegated to the post-processing tools, (i.e., the hardware synthesis tool-chain used to process the Verilog output from CASH). CASH is also not taking full advantage of the immense freedom afforded by the Virtual ISA by using custom operations (except in some modest ways, such as using tokens at runtime (Section 6.5.2) and the token generator operation (Section 4.5.4)). In the simulations presented in this text, CASH ends up by using a rather restricted set of computational primitives, rather similar to the machine code of a contemporary processor (with somewhat fewer limitations on the instruction size, such as the register set or immediate values encoding). Potentially important performance improvements may be unleashed by the use of a truly arbitrary set of computational primitives, as afforded by a truly custom hardware target, as shown in the research about reconfigurable computing.

#### 2.4.2 What CASH Does

With regard to the range of program transformations performed, CASH is much closer to a software compiler than to a CAD tool. We have implemented in CASH most textbook scalar optimizations. In addition, CASH has proven to be a great vehicle for implementing some memory-related optimizations, such as redundancy elimination and register promotion.

Most optimizations in CASH are applied at the level of hyperblocks, which tend to be relatively coarse program regions (see Section 3.3.3). Optimizations are therefore, as effectiveness goes, somewhere between purely local, basic-block-based optimizations, and global, whole-procedure optimizations. While it is very hard to quantify the quality of optimizations in a precise way, we believe that the quality of the code is closer to that achieved by global optimizations than to purely local transformations. An important point is that most innermost loops<sup>8</sup> are hyperblocks and therefore are treated as an optimization unit.

As already discussed, the front-end performs procedure inlining and loop unrolling. The CASH core performs (truly) global constant propagation, constant folding, partial redundancy elimination for both scalars and memory, a wide range of algebraic optimizations, loop-invariant code motion, scalar promotion based on powerful memory disambiguation, strength reduction, unreachable- and dead code removal and Boolean simplifications. The compiler also performs pipeline balancing for enhancing the throughput of the circuits which exhibit dataflow software pipelining.

## 2.5 Compiling C to Hardware

One can find many arguments that C is a strong contender for the title of "worst possible hardware description language." The main argument about using C is its huge installed code base and its undisputed use in systems programming at all levels.

#### 2.5.1 Using C for Spatial Computation

The question arises naturally: if we consider C a "difficult" language for hardware description, why use it in the first place? Our motivations are several:

<sup>&</sup>lt;sup>8</sup>Unless they contain a recursive call, as described in Section 3.3.11.

- The C language has a huge installed code base. This makes CASH a domain-independent compiler, equally applicable for digital signal processing, scientific computation or almost any other domain.

- C is frequently the language of choice for describing reference implementations. Indeed, many complex standards now contain not only textual specifications, but also a sample implementation and criteria for correctness, such as bit-exactness. For example, the General Systems Mobile (GSM) standard for mobile telephony relies on an EFR speech codec defined by the European Telecommunications Standards Institute (ETSI) specifications, which is specified by a reference C program along with a set of testing sequences [Ins]. So CASH can be used as a very fast prototyping tool for implementing custom hardware starting from a specification just feed the source program to CASH and you can obtain a hardware circuit in a matter of man-minutes.

- While some aspects of the compilation process in CASH are specific to C, most of the techniques are equally applicable to other (imperative) programming languages. In fact, the input of the core CASH compiler can be considered the Low Suif representation (see Figure 2.5), which is closer to machine code than to C. Any language that can be translated to three-operand code could therefore be a source for our spatial compiler. Moreover, the freedom that C allows in pointer manipulation makes the translation task harder. Therefore, if CASH works for C, it ought to be easier to extend to other languages. For example, handling FORTRAN would mostly require replacing the algorithm for memory dependence estimation. It is somewhat less obvious whether the translation and optimization methodologies employed in CASH can be successfully applied to an explicitly parallel language, which would arguably be a better source for hardware description.

Some other motivations for using C have more to do with the pragmatics of the research process than with the economics of the solution:

- Choosing such a small and well-understood language, and leveraging existing tools (e.g., Suif) for tedious chores, allows us to focus our effort on the translation process and not on language design or parser implementation.

- Our own expertise is mainly in the area of software compilation, and so we have chosen this approach.

While the trade-offs are certainly different when creating hardware and software artifacts, we believe

that a hardware-design tool-chain looking more, and acting as fast as a software tool-chain, would

bring increased productivity benefits to hardware design. This is already one of the main critical

resources in the design cycle of new devices.

- As described in the introduction, the original motivation of this research is to address the challenge of creating multi-billion device designs by effectively handling complexity. We have therefore generously given ourselves virtually unlimited hardware resources. By constraining the research to the use of C, and making a requirement to handle all language features, we have anchored one end-point of the design space in "reality." This allows us to evaluate the effectiveness of our methodology much better than if we were using a custom designed, special-purpose language.

#### 2.5.2 Related Work

While there is a substantial amount of research on hardware synthesis from high-level languages, and even from dialects of C and C++, none of it supports C as fully as CASH does. One major difference between our approach and the vast majority of the other synthesis from C efforts is the difference in the role of

the language itself. Most projects use C as a hardware description language (HDL), used to describe the functionality of a particular piece of hardware. We are not interested in using C as a description language. We are just interested in *implementing* the C program so that it produces the expected result.

Another way to express the difference between using C as an HDL and our approach is with regard to *reactivity*: hardware designs customarily assume that the environment can change at any moment and that the hardware must react immediately. In contrast, our view of the environment is extremely restricted. Even when CASH compiles only part of a program, it implicitly assumes that there is a single thread of control and that there are no unexpected external changes. The stack (last-in, first-out) nature of procedure invocation/completion is also a typical aspect of software assumed by CASH.

This difference of optics is translated in a different approach. Other projects either add constructs (such as reactivity, concurrency and variable bit-width) to C in order to make it more suitable to expressing hardware properties, or/and remove constructs (such as pointers, dynamic allocation and recursion) which do not correspond to natural hardware objects, obtaining "Register Transfer C." Other efforts impose a strict coding discipline in C in order to obtain a synthesizable program. There are numerous commercial products using variants of C as an HDL [Mic99]: Cynlib from Cynapps [RR00, RR99], Cyber from NEC [Wak99, WO00], A | RT builder, now from Xilinx [Joh99, Joh00], Scenic/CoCentrinc from Synopsis [LTG97, Syn], N2C from CoWare [CoW00], compilers for Bach-C (originally based on Occam) from Sharp [KNY<sup>+</sup>99], OCAPI from IMEC [SVR<sup>+</sup>98], Compilogic's (acquired by Synopsis), System Compiler from C-level Design, (acquired by Synopsis) [ID99], c2verilog [SP98], Celoxica's Handel-C compiler [Cor03], and Cadence's ECL (based on C and Esterel) compiler [LS99]. University research projects include SpC from Stanford [SSM01], PACT from Northwestern [JBP<sup>+</sup>02] and also [GKL99, Arn99, GSD<sup>+</sup>02, GSK<sup>+</sup>01, KC98]. For an interesting appraisal of the effectiveness of many of these tools, see [Coo00].

A completely different approach to hardware design is taken in the research on reconfigurable computing, which relies on automatic compilation of C or other high-level languages to target reconfigurable hardware [Wir98]. Notable projects are: PRISM/PRISM II [AS93, WAL<sup>+</sup>93b], PRISC [RS94], DISC [WH95], NAPA [GM95], DEFACTO [DHP<sup>+</sup>01], Chimaera [YSB00, YMHB00], OneChip [Esp00, WC96], RaPiD [ECF<sup>+</sup>97], PamDC [TS99], StreamC [GSAK00], WASMII [TSI<sup>+</sup>99], XCC/PACT [CW02], the systems described in [SSC01] and [MH00], compilation of Term-Rewriting Systems [HA00], or synthesis of dataflow graphs [RCP<sup>+</sup>01]. Our approach is original because (1) it compiles arbitrary ANSI C programs, without restrictions or extensions; (2) it generates asynchronous, dynamically scheduled circuits; and (3) it generates circuits which implement directly the program, without the use of interpretive structures.

More remotely related is the work on "custom processors", whose goal is to synthesize a domain-specific processor. This is largely a problem of instruction-set design. In this group we can rank the Hewlett-Packard PICO project [SA02, MRS+01, SGR+01], the Tensilica products [WKMR01, Ten], and automatic "super-instruction" selection: [AC01, LCD02, ZWM+01, CTM02, SRV98, WKMR01, LVL03], and many others. PICO handles only a restricted C subset, namely using dense matrix operations. Tensilica processors can be extended with arbitrary instructions, whose behavior is described in a Verilog-like language. These new instructions get automatically incorporated in the hardware and compilation tools. These methods often involve profiling execution traces of existing microprocessors and collapsing repeated patterns in custom instructions.

CASH has been profoundly influenced by the work of Callahan on the GARP C compiler [Cal02, CW98], whose ideas were incorporated in the Nimble compiler [LCD+00]. GarpCC is still one of the

<sup>&</sup>lt;sup>9</sup>Of course, some of the standard C language mechanisms, such as volatile qualifiers, can be used in the same way as in system code to prevent optimizations from relying too much on the model of single thread of control when external effects need to be modeled.

systems with the broadest scope targeting C to a reconfigurable fabric.

Our goals are most closely related to the "chip-in-a-day" project from Berkeley [DZC<sup>+</sup>02], but our approach is very different: that project starts from parallel statechart descriptions and employs sophisticated hard macros to synthesize synchronous designs with automatic clock gating. In contrast we start from C, use a small library of standard cells, and build asynchronous circuits.

ASH circuits are somewhat more remotely related to other exotic computational models, such as WaveScalar [SMO03], the grid processor TRIPS [SNBK01], RAW [LBF<sup>+</sup>98], SmartMemories [MPJ<sup>+</sup>00], Imagine [RDK<sup>+</sup>98], and PipeRench [GSM<sup>+</sup>99].

#### 2.5.3 Limitations

The current incarnation of CASH should be able to handle almost any portable legal C program, including pointers, structures, unions, and recursive functions. However, the following C constructs are not yet supported:

- Library functions. We do not compile the library functions, although they may account for a substantial part of the program execution time. ASH has no notion of I/O or system calls, so the library functions handling these could not be mapped to ASH anyway. In simulations we assume that the time spent in library functions is zero, both for ASH and for the baseline processors we consider.

- alloca(), the stack-based memory allocator. There is no fundamental reason alloca cannot be handled and support for it should appear in CASH soon.

- Functions with variable arguments (varargs). Again, there is no fundamental reason CASH cannot support varargs. Implementing varargs however will require a different parameter-passing implementation since CASH currently does never pass arguments on the stack.

- Exceptions, signal() and exit(): see below for a discussion of these interrelated subjects.

- setjmp and longjmp are not handled at all. longjmp could be handled by using an exception-handling mechanism to unwind the stack; setjmp would probably require the same kind of machinery as for saving the complete state of a recursive procedure, described in Section 3.3.11.

#### 2.5.3.1 Exception Handling

Strictly speaking, the C language does not have any exception model. The semantics of a program that causes exceptions is left undefined by the C standard. CASH guarantees to never introduce exceptions which did not exist in the original program. If the source program executes safely, the compiled program should also do so. However, as many other C optimizing compilers do, CASH may remove some exceptions. For example, the register promotion algorithm may store variables in registers rather than memory, causing the optimized program to perform only a subset of the memory accesses of the source program. Currently we assume that run-time exceptions terminate the program.

Handling asynchronous function invocations (as does signal() in C) in Spatial Computation seems to be a very difficult task. In C the whole infrastructure for signal delivery and handling is really hidden within a substantial run-time support piece of machinery, usually built within the operating system kernel.

Exceptions are however important and need to addressed; at the very least, an exception should cause a clean program shutdown. It is not entirely obvious how shutdown (or reset) is to be achieved in the distributed computation structure of Spatial Computation.

A possible solution is to explicitly encode exceptions as control-flow within the program before proceeding to the program transformation and optimization. Exception handling done this way is likely to have a major impact on the efficiency of the generated code and may inhibit or complicate the task of some optimizations because potentially almost any memory access operation can generate an exception. A careful implementation would probably use some sort of "batch processing" of exceptions, accumulating exceptions, checking relatively infrequently for exceptions and following a special execution path on exception detection. Function return values would need to be augmented to indicate the occurrence of exceptions in callees, to allow them to propagate through call chains.

At the very least, exception support is required for implementing the seemingly banal exit() function. As with signal(), the machinery behind exit() in a processor-based system is very complicated, involving the process destruction and resource reclaiming. A natural solution is to handle exit() as a synchronous, program-generated fatal exception and implement it in the way described above.

### 2.6 Code Complexity

By all measures, the core CASH is a small compiler. Table 2.1 shows the amount of source code used for the various parts of CASH, including the front-end, the back-ends and the libraries, as counted by the sloccount [Whe01] utility which ignores white spaces and comments. The line count for the libraries is only approximate since CASH does not always use the full functionality provided by each library. The first line of this table refers to the compiler components described in this thesis. The "build and optimize core" includes all the code described in Section 3.3, used to translate from a CFG representation to Pegasus, and all optimizations described in Chapter 4. A further breakdown of the code complexity for each optimization is presented in Table 4.1 in Section 4.1. The "build and optimize" core is the result of about 2.5 man-years of effort.

## 2.7 Compilation Speed

In this section we compare the compilation speed of CASH and gcc 2.95.1. The procedure is as follows:

- We disable inlining and loop unrolling in both compilers to control the code size, which has a direct bearing on the compilation speed.

- We compile with maximum set of optimizations enabled with both compilers. We use gcc -O2, since according to the gcc manual, it involves all optimizations except unrolling and inlining.

- For CASH we do not time the Suif front-end since it performs no useful operations in this configuration (except parsing). Since the front-end passes communicate through files, timing them would introduce too much noise.

- We stop compilation at the assembly level for gcc.

- We measure the complete compilation process end-to-end. Both compilers are fed all source files on a single command-line.

<sup>&</sup>lt;sup>10</sup>For example, at the end of each hyperblock.

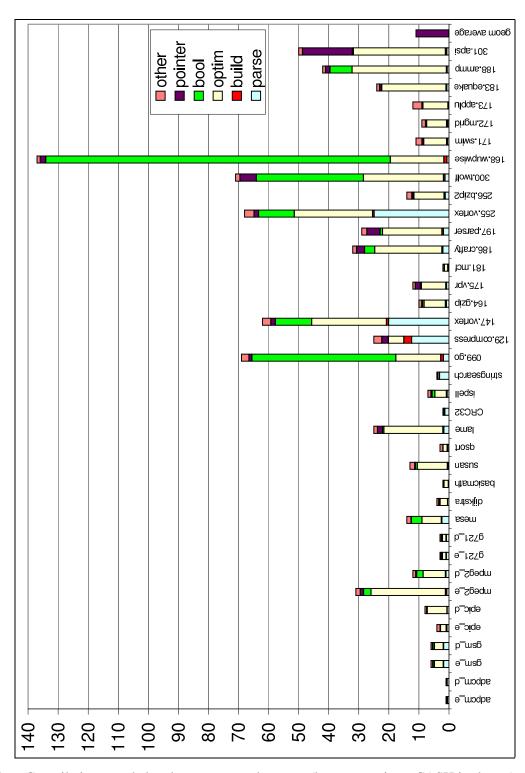

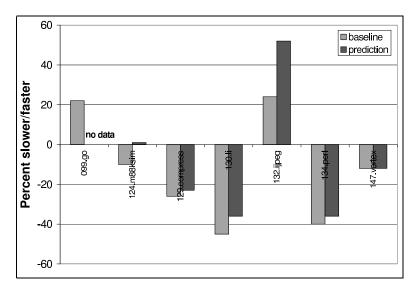

Figure 2.6: Compilation speed slowdown compared to gcc (how many times CASH is slower). The time is broken down into: parsing the Suif intermediate representation, building the Pegasus representation, optimizations except Boolean simplification, Boolean simplification, intra-procedural flow-sensitive pointer analysis and other time (i.e., file I/O, code generation).

| Part      | Functionality                                 | LOC    | Imported |

|-----------|-----------------------------------------------|--------|----------|

| Core      | Build and optimize                            | 15,517 |          |

|           | gcc code                                      | 768    | Y        |

|           | Verilog back-end                              | 9.800  |          |

|           | dot back-end                                  | 444    |          |

|           | C back-end (based on Suif scc)                | 9,416  | Y        |

| Libraries | data structures and CFG and dataflow analyses | 14,815 |          |

|           | Espresso Boolean minimization                 | 11,457 | Y        |

|           | Suif library suif1                            | 16,434 | Y        |

|           | Suif library useful                           | 18,022 | Y        |

| Front-end | Suif scc/snoot (parsing)                      | 14,540 | Y        |

|           | Suif porky (lowering)                         | 16,679 | Y        |

|           | Suif linking (linksuif)                       | 2,352  | Y        |

|           | inlining                                      | 789    | Y        |

|           | loop unrolling                                | 6,470  | Y        |

|           | call-graph                                    | 172    |          |

| Total     | Locally developed code                        | 40,784 |          |

Table 2.1: C++ source lines of code in CASH v2.0. "Imported" code was developed elsewhere.

- gcc does some extra work compared to CASH in this setup. It performs parsing (which in CASH is done by the Suif front-end)<sup>11</sup>, instruction selection, register allocation and scheduling.

- We only display the programs for which CASH has compiled all functions. As described in Section 2.5.3, functions with variable arguments or functions calling alloca were excluded from the CASH compilation.

- We also compile some FORTRAN programs after translating them to C with f2c.

- CASH takes advantage of the call-graph to skip compilation of the unreachable functions.

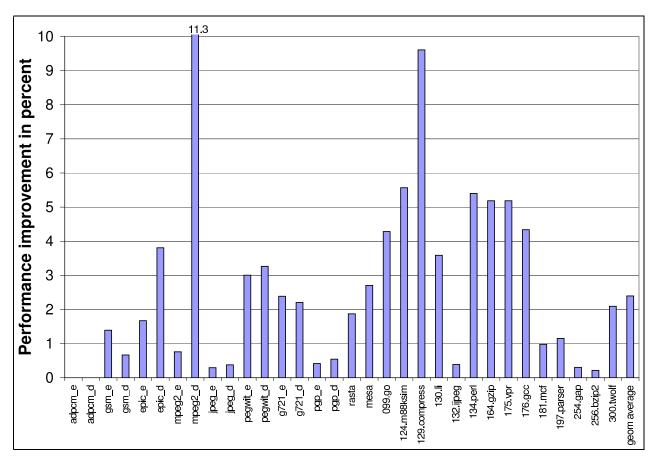

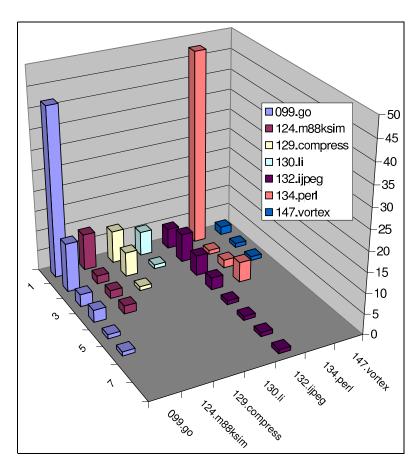

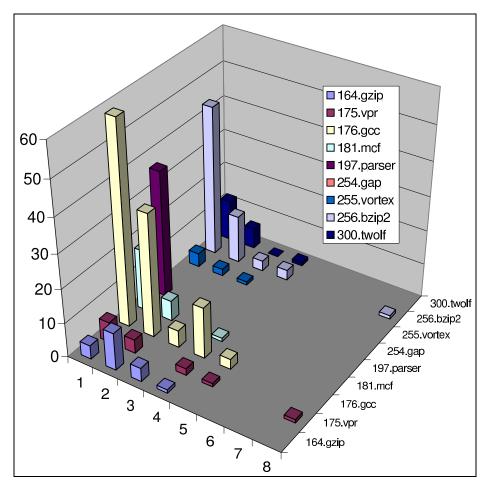

Figure 2.6 shows that CASH is a relatively slow compiler. On average it is about 11 times slower than gcc, but it can be as much as 137 times slower! Looking at the breakdown of the compilation time, we notice that the three slowest programs (168.wupwise,099.go and 300.twolf) spend a lot of time in Boolean minimization. In fact, the 168.wupwise outlier spends almost all its Boolean minimization in processing a single moderately large Boolean expression with 15 inputs and 21 outputs. In general the Boolean minimizer Espresso, which we are using, (which has been designed for hardware logic minimization), has behaved very well by minimizing much larger formulas quickly.

The next two slowest programs are two different versions of vortex, 147 from SpecInt95 and 255 from SpecInt2K. Both these programs spend an inordinate amount of time in parsing the Suif intermediate file before even reaching the build phase (129.compress also spends more than half of its time in parsing). The abnormal parsing times are due to the inefficient data structures and procedures used by Suif for merging the symbol tables of several files.

<sup>&</sup>lt;sup>11</sup>However, even parsing the Suif intermediate files is a very time-consuming operation, sometimes much slower than parsing the original text files. It is unlikely that parsing unjustly penalizes gcc.

Finally, the sixth worst program (301.apsi) spends one third of its time in pointer analysis. If we discount these extreme examples, for all programs most of the time is spent in optimization. We have not explored trade-offs between compilation time and code quality.

# **Chapter 3**

# **Pegasus: a Dataflow Internal Representation**

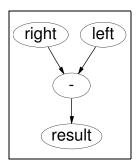

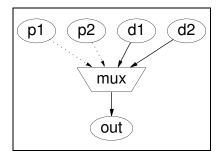

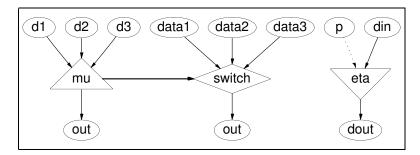

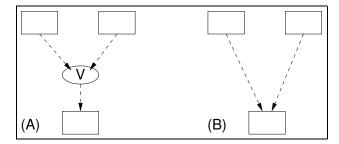

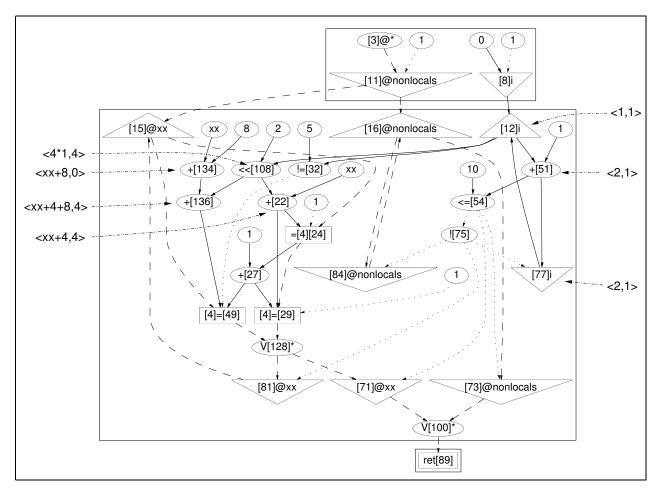

#### 3.1 Introduction

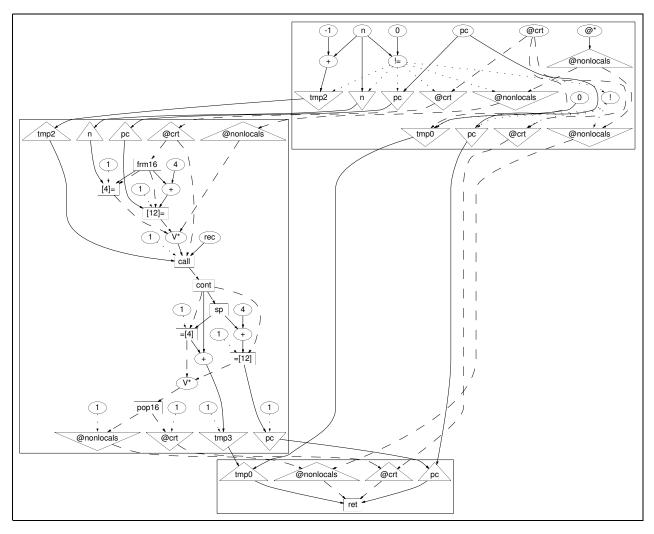

The original motivation for this research was the creation of a C compiler, CASH, which translates programs into hardware circuits. Pegasus is the internal representation of CASH. During the compiler development the intended target has guided many of the design decisions. We think that it is easier for the reader to follow the details of this representation if the explicit connection to actual hardware is kept in mind. Probably the most important feature of Pegasus from this point of view is its *completeness* — the representation is self-contained, enabling a complete synthesis of the circuits, without requiring further information. Internal representations with this property are called *executable* [PBJ<sup>+</sup>91]. The naming suggests that one can write an interpreter for executing such a representation.